COP888 Feature Family User's Manual

Customer Order Number COP8-888FAM-MAN NSC Publication Number 420411060-001B July 1994

# REVISION RECORD

| REVISION | RELEASE DATE | SUMMARY OF CHANGES                                                                                       |

|----------|--------------|----------------------------------------------------------------------------------------------------------|

| A        | 03/89        | First Release<br>COP888 User's Manual<br>NSC Publication Number 420411060-001A                           |

| В        | 07/94        | Reformatted and updated manual to include information on new devices added to the COP888 Feature Family. |

## **PREFACE**

The COP888 Feature Family of 8-bit microcontrollers is ideally suited to embedded controller applications such as keyboard interfaces, electronic telephones, home appliances, and ABS systems. The design of this family takes advantage of National Semiconductor's M²CMOS™ manufacturing technology, providing a useful combination of high performance, low power consumption, and reasonable cost. The rich instruction set and flexible addressing modes of the COP888 controllers contribute to their high performance and code efficiency.

This manual describes the features, architecture, instruction set, and usage of the COP888 microcontrollers. The beginning chapters describe the general features found in all family members. Later chapters describe the individual family members and their specific features. The following specific devices are covered:

- COP888CL

- COP888CG/EG/CS

- COP888CF

Chapter 1, OVERVIEW, provides an overview of the COP888 family and compares the features of different family members.

Chapter 2, ARCHITECTURE, describes the overall architecture of the COP888 microcontroller, including the CPU core, registers, memory organization, reset operation, and clock options.

Chapter 3, INTERRUPTS, describes the device interrupts and how they are used. The types of interrupts vary from one family member to another.

Chapter 4, TIMERS, describes the on-chip timers and their operating modes. The number and types of timers vary from one family member to another.

Chapter 5, MICROWIRE/PLUS, describes the microcontroller's MICROWIRE/PLUS serial interface and its operating modes.

Chapter 6, POWER SAVE MODES, describes the special operating modes in which the microcontroller is shut down, reducing power consumption to a very low value while maintaining the processor status and all register contents. All family members have a HALT mode, and some also have an IDLE mode that maintains real time while the processor is shut down.

Chapter 7, INPUT/OUTPUT, describes the input/output ports of the microcontroller and how they are used. The number and types of ports vary from one family member to another.

Chapter 8, WATCHDOG AND CLOCK MONITOR, describes an internal circuit available in some COP888 devices that monitors the operation of the microcontroller and reports an abnormal condition by issuing a signal on an output pin.

Chapter 9, INSTRUCTION SET, describes the instruction set of the COP888 microcontrollers, including detailed descriptions of each instruction.

Chapters 10, 11, and 12 describe the specific features of different COP888 Feature Family members.

Chapter 13, APPLICATION HINTS, provides additional information that may be useful in implementing a design.

The Appendices cover hardware development tools, emulation devices, and device electrical characterization data.

Additional information on specific COP888 Feature Family members is available from their respective data sheets.

The information contained in this manual is for reference only and is subject to change without notice.

No part of this document may be reproduced in any form or by any means without the prior written consent of National Semiconductor Corporation.

COPS, M<sup>2</sup>CMOS are trademarks of National Semiconductor Corporation.

## **CONTENTS**

| Chapter 1 | OVERVIEW                                   |      |

|-----------|--------------------------------------------|------|

| 1.1       | INTRODUCTION                               | 1-1  |

| 1.2       | BASIC FEATURES                             | 1-1  |

| 1.3       | DEVICE-SPECIFIC FEATURES                   | 1-2  |

| Chapter 2 | ARCHITECTURE                               |      |

| 2.1       | INTRODUCTION                               | 2-1  |

| 2.2       | BLOCK DIAGRAM                              | 2-1  |

| 2.3       | MEMORY ORGANIZATION                        | 2-2  |

|           | 2.3.1 Program Memory                       | 2-3  |

|           | 2.3.2 Data Memory                          | 2-3  |

|           | 2.3.3 Memory-Mapped I/O Registers          | 2-7  |

| 2.4       | CORE REGISTERS                             | 2-8  |

|           | 2.4.1 Accumulator                          | 2-8  |

|           | 2.4.2 Program Counter                      | 2-9  |

|           | 2.4.3 Control Registers                    | 2-9  |

|           | 2.4.4 Data Registers                       | 2-10 |

|           | 2.4.5 MICROWIRE/PLUS Register              | 2-12 |

|           | 2.4.6 Timer Registers                      | 2-12 |

| 2.5       | CPU OPERATION                              | 2-12 |

|           | 2.5.1 Memory Fetches                       | 2-14 |

|           | 2.5.2 Instruction Decoding and Execution   | 2-15 |

|           | 2.5.3 Interrupt and Error Handling         | 2-20 |

| 2.6       | RESET                                      | 2-21 |

| 2.7       | CLOCK OPTIONS                              | 2-22 |

|           | 2.7.1 Crystal Oscillator                   | 2-22 |

|           | 2.7.2 RC Oscillator                        | 2-23 |

| Chapter 3 |                                            |      |

| 3.1       | INTRODUCTION                               | 3-1  |

| 3.2       | VIS INSTRUCTION AND VECTOR TABLE           | 3-2  |

| 3.3       | CONTEXT SWITCHING                          | 3-4  |

| 3.4       | MASKABLE INTERRUPTS                        | 3-5  |

| 3.5       | NON-MASKABLE INTERRUPTS                    | 3-7  |

|           | 3.5.1 Non-Maskable Interrupt Pending Flags | 3-7  |

|           | 3.5.2 Software Trap                        | 3-8  |

|           | 3.5.3 NMI                                  | 3-9  |

|           | 3.5.4 Software Trap and NMI Interaction    | 3-9  |

| 3.6       | INTERRUPT SUMMARY                          | 3-10 |

| Chapter 4 | TIMERS                                     |      |

| 4.1       | INTRODUCTION                               | 4-1  |

| 4.2       | TIMER/COUNTER BLOCK                        | 4-1  |

| 4.3       | TIMER CONTROL BITS                         | 4-2  |

| 4.4       | TIMER OPERATING MODES                      | 4-3  |

|           | 4.4.1 PWM Mode                             | 4-4  |

|           | 4.4.2 External Event Counter Mode          | 4-5  |

|                                                                                                                     | 4.4.3 Input Capture Mode                                                                                                                                                                                                                                                                                                                                   | 4-7                                                                                     |

|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 4.5                                                                                                                 | ADDITIONAL GENERAL-PURPOSE TIMERS                                                                                                                                                                                                                                                                                                                          | 4-10                                                                                    |

| 4.6                                                                                                                 | IDLE TIMER                                                                                                                                                                                                                                                                                                                                                 | 4-11                                                                                    |

| Chapter 5                                                                                                           | MICROWIRE/PLUS                                                                                                                                                                                                                                                                                                                                             |                                                                                         |

| 5.1                                                                                                                 | INTRODUCTION                                                                                                                                                                                                                                                                                                                                               | 5-1                                                                                     |

| 5.2                                                                                                                 | THEORY OF OPERATION                                                                                                                                                                                                                                                                                                                                        | 5-2                                                                                     |

| 0.2                                                                                                                 | 5.2.1 Timing                                                                                                                                                                                                                                                                                                                                               | 5-2<br>5-2                                                                              |

|                                                                                                                     | 5.2.2 Port G Configuration                                                                                                                                                                                                                                                                                                                                 | 5-4                                                                                     |

|                                                                                                                     | 5.2.3 SK Clock Frequency                                                                                                                                                                                                                                                                                                                                   | 5-4<br>5-4                                                                              |

|                                                                                                                     | 5.2.4 Busy Flag and Interrupt                                                                                                                                                                                                                                                                                                                              | 5- <del>4</del><br>5-5                                                                  |

| 5.3                                                                                                                 | MASTER MODE OPERATION EXAMPLE                                                                                                                                                                                                                                                                                                                              | 5-6                                                                                     |

| 5.4                                                                                                                 | SLAVE MODE OPERATION EXAMPLE                                                                                                                                                                                                                                                                                                                               | 5-0<br>5-7                                                                              |

|                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                            | 5-7                                                                                     |

| Chapter 6                                                                                                           | POWER SAVE MODES                                                                                                                                                                                                                                                                                                                                           |                                                                                         |

| 6.1                                                                                                                 | INTRODUCTION                                                                                                                                                                                                                                                                                                                                               | 6-1                                                                                     |

| 6.2                                                                                                                 | ENTERING THE HALT MODE                                                                                                                                                                                                                                                                                                                                     | 6-1                                                                                     |

|                                                                                                                     | 6.2.1 Clock-Stopping Method                                                                                                                                                                                                                                                                                                                                | 6-1                                                                                     |

|                                                                                                                     | 6.2.2 Port G Method                                                                                                                                                                                                                                                                                                                                        | 6-2                                                                                     |

| 6.3                                                                                                                 | EXITING THE HALT MODE                                                                                                                                                                                                                                                                                                                                      | 6-2                                                                                     |

|                                                                                                                     | 6.3.1 HALT Exit Using Reset                                                                                                                                                                                                                                                                                                                                | 6-2                                                                                     |

|                                                                                                                     | 6.3.2 HALT Exit Using Multi-Input Wakeup                                                                                                                                                                                                                                                                                                                   | 6-2                                                                                     |

|                                                                                                                     | 6.3.3 HALT Exit Using G7 Pin                                                                                                                                                                                                                                                                                                                               | 6-3                                                                                     |

| 6.4                                                                                                                 | IDLE MODE                                                                                                                                                                                                                                                                                                                                                  | 6-3                                                                                     |

| 6.5                                                                                                                 | HALT/IDLE AND WATCHDOG OPERATION                                                                                                                                                                                                                                                                                                                           | 6-4                                                                                     |

| 6.6                                                                                                                 | NMI EXIT FROM HALT/IDLE                                                                                                                                                                                                                                                                                                                                    | 6-4                                                                                     |

| Chapter 7                                                                                                           | INPUT/OUTPUT                                                                                                                                                                                                                                                                                                                                               |                                                                                         |

|                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                            |                                                                                         |

| 7.1                                                                                                                 | INTRODUCTION                                                                                                                                                                                                                                                                                                                                               | 7-1                                                                                     |

| 7.1 $7.2$                                                                                                           | INTRODUCTION                                                                                                                                                                                                                                                                                                                                               | 7-1<br>7-2                                                                              |

| 7.2                                                                                                                 | PORT C                                                                                                                                                                                                                                                                                                                                                     | 7-2                                                                                     |

|                                                                                                                     | PORT C                                                                                                                                                                                                                                                                                                                                                     | 7-2<br>7-2                                                                              |

| 7.2<br>7.3                                                                                                          | PORT C                                                                                                                                                                                                                                                                                                                                                     | 7-2<br>7-2<br>7-3                                                                       |

| 7.2<br>7.3<br>7.4                                                                                                   | PORT C                                                                                                                                                                                                                                                                                                                                                     | 7-2<br>7-2<br>7-3<br>7-3                                                                |

| 7.2<br>7.3<br>7.4<br>7.5<br>7.6                                                                                     | PORT C PORT D PORT G PORT I. PORT L                                                                                                                                                                                                                                                                                                                        | 7-2<br>7-2<br>7-3<br>7-3<br>7-3                                                         |

| 7.2<br>7.3<br>7.4<br>7.5                                                                                            | PORT C PORT D PORT G PORT I PORT L ALTERNATE FUNCTIONS                                                                                                                                                                                                                                                                                                     | 7-2<br>7-2<br>7-3<br>7-3<br>7-3<br>7-4                                                  |

| 7.2<br>7.3<br>7.4<br>7.5<br>7.6                                                                                     | PORT C PORT D PORT G PORT I PORT L ALTERNATE FUNCTIONS 7.7.1 Port G Alternate Functions                                                                                                                                                                                                                                                                    | 7-2<br>7-2<br>7-3<br>7-3<br>7-3<br>7-4<br>7-4                                           |

| 7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7                                                                              | PORT C PORT D PORT G PORT I PORT L ALTERNATE FUNCTIONS 7.7.1 Port G Alternate Functions 7.7.2 Multi-Input Wakeup/Interrupt                                                                                                                                                                                                                                 | 7-2<br>7-2<br>7-3<br>7-3<br>7-3<br>7-4                                                  |

| 7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7                                                                              | PORT C                                                                                                                                                                                                                                                                                                                                                     | 7-2<br>7-2<br>7-3<br>7-3<br>7-3<br>7-4<br>7-4                                           |

| 7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>Chapter 8</b><br>8.1                                                   | PORT C                                                                                                                                                                                                                                                                                                                                                     | 7-2<br>7-2<br>7-3<br>7-3<br>7-3<br>7-4<br>7-4<br>7-4                                    |

| 7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>Chapter 8</b><br>8.1<br>8.2                                            | PORT C PORT D PORT G PORT I PORT L ALTERNATE FUNCTIONS 7.7.1 Port G Alternate Functions 7.7.2 Multi-Input Wakeup/Interrupt WATCHDOG AND CLOCK MONITOR INTRODUCTION WATCHDOG OPERATION                                                                                                                                                                      | 7-2<br>7-2<br>7-3<br>7-3<br>7-3<br>7-4<br>7-4<br>7-4<br>8-1<br>8-1                      |

| 7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>Chapter 8</b><br>8.1<br>8.2<br>8.3                                     | PORT C PORT D PORT G PORT I PORT I PORT L ALTERNATE FUNCTIONS 7.7.1 Port G Alternate Functions 7.7.2 Multi-Input Wakeup/Interrupt WATCHDOG AND CLOCK MONITOR INTRODUCTION WATCHDOG OPERATION CLOCK MONITOR OPERATION                                                                                                                                       | 7-2<br>7-2<br>7-3<br>7-3<br>7-3<br>7-4<br>7-4<br>7-4<br>8-1<br>8-1<br>8-3               |

| 7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>Chapter 8</b><br>8.1<br>8.2<br>8.3<br>8.4                              | PORT C PORT D PORT G PORT G PORT I PORT L ALTERNATE FUNCTIONS 7.7.1 Port G Alternate Functions 7.7.2 Multi-Input Wakeup/Interrupt WATCHDOG AND CLOCK MONITOR INTRODUCTION WATCHDOG OPERATION CLOCK MONITOR OPERATION CONFIGURATION                                                                                                                         | 7-2<br>7-3<br>7-3<br>7-3<br>7-4<br>7-4<br>7-4<br>8-1<br>8-1<br>8-3<br>8-3               |

| 7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>Chapter 8</b><br>8.1<br>8.2<br>8.3                                     | PORT C PORT D PORT G PORT I PORT I ALTERNATE FUNCTIONS 7.7.1 Port G Alternate Functions 7.7.2 Multi-Input Wakeup/Interrupt WATCHDOG AND CLOCK MONITOR INTRODUCTION WATCHDOG OPERATION CLOCK MONITOR OPERATION CONFIGURATION ERROR REPORT ON WDOUT                                                                                                          | 7-2<br>7-2<br>7-3<br>7-3<br>7-3<br>7-4<br>7-4<br>7-4<br>8-1<br>8-1<br>8-3               |

| 7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>Chapter 8</b><br>8.1<br>8.2<br>8.3<br>8.4                              | PORT C PORT D PORT G PORT I PORT I ALTERNATE FUNCTIONS 7.7.1 Port G Alternate Functions 7.7.2 Multi-Input Wakeup/Interrupt WATCHDOG AND CLOCK MONITOR INTRODUCTION WATCHDOG OPERATION CLOCK MONITOR OPERATION CONFIGURATION ERROR REPORT ON WDOUT INSTRUCTION SET                                                                                          | 7-2<br>7-3<br>7-3<br>7-3<br>7-4<br>7-4<br>7-4<br>8-1<br>8-1<br>8-3<br>8-3               |

| 7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>Chapter 8</b> 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br><b>Chapter 9</b> 9.1  | PORT C PORT D PORT G PORT I PORT I ALTERNATE FUNCTIONS 7.7.1 Port G Alternate Functions 7.7.2 Multi-Input Wakeup/Interrupt WATCHDOG AND CLOCK MONITOR INTRODUCTION WATCHDOG OPERATION CLOCK MONITOR OPERATION CONFIGURATION ERROR REPORT ON WDOUT INSTRUCTION SET INTRODUCTION                                                                             | 7-2<br>7-3<br>7-3<br>7-3<br>7-4<br>7-4<br>7-4<br>8-1<br>8-1<br>8-3<br>8-3               |

| 7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>Chapter 8</b> 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br><b>Chapter 9</b>      | PORT C PORT D PORT G PORT I PORT I ALTERNATE FUNCTIONS 7.7.1 Port G Alternate Functions 7.7.2 Multi-Input Wakeup/Interrupt WATCHDOG AND CLOCK MONITOR INTRODUCTION WATCHDOG OPERATION CLOCK MONITOR OPERATION CONFIGURATION ERROR REPORT ON WDOUT INSTRUCTION SET INTRODUCTION INSTRUCTION FEATURES                                                        | 7-2<br>7-3<br>7-3<br>7-3<br>7-4<br>7-4<br>7-4<br>8-1<br>8-3<br>8-3<br>8-5               |

| 7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>Chapter 8</b> 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br><b>Chapter 9</b> 9.1  | PORT C PORT D PORT G PORT I PORT I ALTERNATE FUNCTIONS 7.7.1 Port G Alternate Functions 7.7.2 Multi-Input Wakeup/Interrupt WATCHDOG AND CLOCK MONITOR INTRODUCTION WATCHDOG OPERATION CLOCK MONITOR OPERATION CONFIGURATION ERROR REPORT ON WDOUT INSTRUCTION SET INTRODUCTION INSTRUCTION FEATURES ADDRESSING MODES                                       | 7-2<br>7-3<br>7-3<br>7-3<br>7-4<br>7-4<br>7-4<br>8-1<br>8-3<br>8-3<br>8-5               |

| 7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>Chapter 8</b> 8.1<br>8.2<br>8.3<br>8.4<br>8.5 <b>Chapter 9</b> 9.1 9.2 | PORT C PORT D PORT G PORT G PORT I PORT L ALTERNATE FUNCTIONS 7.7.1 Port G Alternate Functions 7.7.2 Multi-Input Wakeup/Interrupt WATCHDOG AND CLOCK MONITOR INTRODUCTION WATCHDOG OPERATION CLOCK MONITOR OPERATION CONFIGURATION ERROR REPORT ON WDOUT INSTRUCTION SET INTRODUCTION INSTRUCTION FEATURES ADDRESSING MODES 9.3.1 Operand Addressing Modes | 7-2<br>7-3<br>7-3<br>7-3<br>7-4<br>7-4<br>7-4<br>8-1<br>8-1<br>8-3<br>8-3<br>8-5        |

| 7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br><b>Chapter 8</b> 8.1<br>8.2<br>8.3<br>8.4<br>8.5 <b>Chapter 9</b> 9.1 9.2 | PORT C PORT D PORT G PORT I PORT I ALTERNATE FUNCTIONS 7.7.1 Port G Alternate Functions 7.7.2 Multi-Input Wakeup/Interrupt WATCHDOG AND CLOCK MONITOR INTRODUCTION WATCHDOG OPERATION CLOCK MONITOR OPERATION CONFIGURATION ERROR REPORT ON WDOUT INSTRUCTION SET INTRODUCTION INSTRUCTION FEATURES ADDRESSING MODES                                       | 7-2<br>7-3<br>7-3<br>7-3<br>7-4<br>7-4<br>7-4<br>8-1<br>8-3<br>8-3<br>8-5<br>9-1<br>9-1 |

vi

| 9.5 |                  | RENCES BETWEEN COP800 AND COP888 LED FUNCTIONAL DESCRIPTIONS OF INSTRUCTIONS | 9-9          |

|-----|------------------|------------------------------------------------------------------------------|--------------|

| 9.6 |                  |                                                                              | 9-10<br>9-13 |

|     | 9.6.1            | ADD Add with Carry                                                           |              |

|     | 9.6.2            | AND And                                                                      | 9-14         |

|     | 9.6.3            | AND—And                                                                      | 9-15         |

|     | 9.6.4            | ANDSZ — And, Skip if Zero                                                    | 9-16         |

|     | 9.6.5            | CLR — Clear Accumulator                                                      | 9-17         |

|     | 9.6.6            | DCOR — Decimal Correct                                                       | 9-18         |

|     | 9.6.7            | DEC — Decrement Accumulator                                                  | 9-19         |

|     | 9.6.8            | DRSZ REG# — Decrement Register and Skip if Result                            | 0.00         |

|     | 0.00             | is Zero                                                                      | 9-20         |

|     | 9.6.9            | IFBIT — Test Bit                                                             | 9-21         |

|     | 9.6.10           | IFBNE # — If B Pointer Not Equal                                             | 9-22         |

|     | 9.6.11           | IFC — Test if Carry                                                          | 9-23         |

|     | 9.6.12           | IFEQ — Test if Equal                                                         | 9-24         |

|     | 9.6.13           | IFGT — Test if Greater Than                                                  | 9-25         |

|     | 9.6.14           | IFNC — Test If No Carry                                                      | 9-26         |

|     | 9.6.15           | IFNE — Test If Not Equal                                                     | 9-27         |

|     | 9.6.16           | INC — Increment Accumulator                                                  | 9-28         |

|     | 9.6.17           | INTR — Interrupt (Software Trap)                                             | 9-29         |

|     | 9.6.18           | JID — Jump Indirect                                                          | 9-30         |

|     | 9.6.19           | JMP — Jump Absolute                                                          | 9-31         |

|     | 9.6.20           | JMPL — Jump Absolute Long                                                    | 9-32         |

|     | 9.6.21           | JP — Jump Relative                                                           | 9-33         |

|     | 9.6.22           | JSR — Jump Subroutine                                                        | 9-34         |

|     | 9.6.23           | JSRL — Jump Subroutine Long                                                  | 9-35         |

|     | 9.6.24           | LAID — Load Accumulator Indirect                                             | 9-36         |

|     | 9.6.25           | LD — Load Accumulator                                                        | 9-37         |

|     | 9.6.26           | LD — Load B Pointer                                                          | 9-39         |

|     | 9.6.27           | LD — Load Memory                                                             | 9-40         |

|     | 9.6.28           | LD — Load Register                                                           | 9-41         |

|     | 9.6.29           | NOP — No Operation                                                           | 9-42         |

|     | 9.6.30           | OR — Or                                                                      | 9-43         |

|     | 9.6.31           | POP — Pop Stack                                                              | 9-44         |

|     | 9.6.32           | PUSH — Push Stack                                                            | 9-45         |

|     | 9.6.33           | RBIT — Reset Memory Bit                                                      | 9-46         |

|     | 9.6.34           | RC — Reset Carry                                                             | 9-47         |

|     | 9.6.35           | RET — Return from Subroutine                                                 | 9-48         |

|     | 9.6.36           | RETI — Return from Interrupt                                                 | 9-49         |

|     | 9.6.37           | RETSK — Return and Skip                                                      | 9-50         |

|     | 9.6.38           | RLC — Rotate Accumulator Left Through Carry                                  | 9-51         |

|     | 9.6.39           | RPND — Reset Pending                                                         | 9-52         |

|     | 9.6.40           | RRC — Rotate Accumulator Right Through Carry                                 | 9-53         |

|     | 9.6.40           | SBIT — Set Memory Bit                                                        | 9-54         |

|     | 9.6.41           | SC — Set Carry                                                               | 9-55         |

|     | 9.6.42 $9.6.43$  | SUBC — Set Carry                                                             | 9-56         |

|     | 9.6.43           | SWAP — Swap Nibbles of Accumulator                                           | 9-58         |

|     | 9.6.44 $9.6.45$  | VIS — Vector Interrupt Select                                                | 9-59         |

|     | 9.6.46           | X — Exchange Memory with Accumulator                                         | 9-60         |

|     | 9.6.46<br>9.6.47 | XOR — Exclusive Or                                                           | 9-60         |

|     | 204/             | AUD — PACIDAIVE OF                                                           | .J-().Z      |

| 9.7<br>9.8    | INSTRUCTION OPERATIONS SUMMARY          | 9-63<br>9-64 |

|---------------|-----------------------------------------|--------------|

| Chapter 10    |                                         |              |

| 10.1          | INTRODUCTION                            | 10-1         |

| 10.1          | BLOCK DIAGRAM                           | 10-1         |

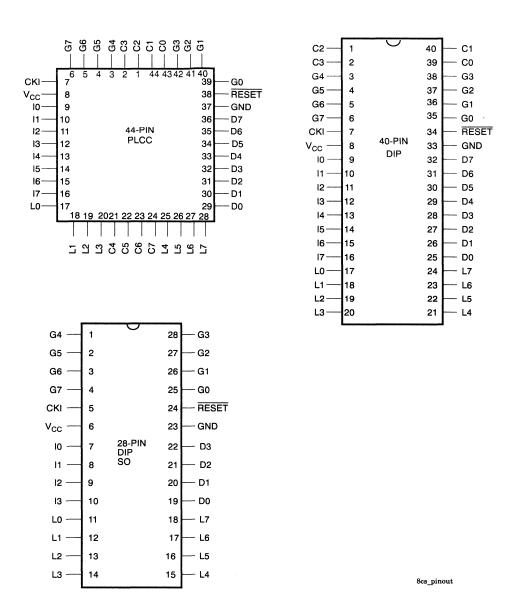

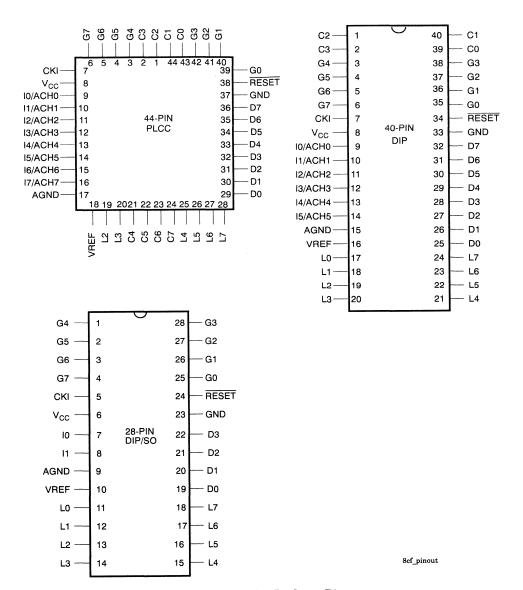

| 10.2          | DEVICE PINOUTS/PACKAGES                 | 10-1         |

| 10.3          | PIN DESCRIPTIONS.                       | 10-2         |

| 10.5          | INPUT/OUTPUT PORTS.                     | 10-2         |

| 10.6          | PROGRAM MEMORY                          | 10-5         |

| 10.7          | DATA MEMORY.                            | 10-0         |

| 10.7          | REGISTER BIT MAPS.                      | 10-7         |

| 10.8          | MEMORY MAP.                             | 10-7         |

| 10.3          | RESET                                   | 10-9         |

| 10.10         | INTERRUPTS.                             | 10-10        |

| 10.11 $10.12$ | MASK OPTIONS                            | 10-11        |

| 10.12         | EMULATION DEVICES                       | 10-12        |

|               |                                         | 10-19        |

| Chapter 1     |                                         |              |

| 11.1          | INTRODUCTION                            | 11-1         |

| 11.2          | BLOCK DIAGRAMS                          | 11-2         |

| 11.3          | DEVICE PINOUTS/PACKAGES                 | 11-3         |

| 11.4          | PIN DESCRIPTIONS                        | 11-3         |

| 11.5          | INPUT/OUTPUT PORTS                      | 11-6         |

| 11.6          | PROGRAM MEMORY                          | 11-7         |

| 11.7          | DATA MEMORY                             | 11-8         |

| 11.8          | REGISTER BIT MAPS                       | 11-8         |

| 11.9          | MEMORY MAP                              | 11-13        |

| 11.10         | RESET                                   | 11-15        |

| 11.11         | INTERRUPTS                              | 11-16        |

| 11.12         | COMPARATOR                              | 11-16        |

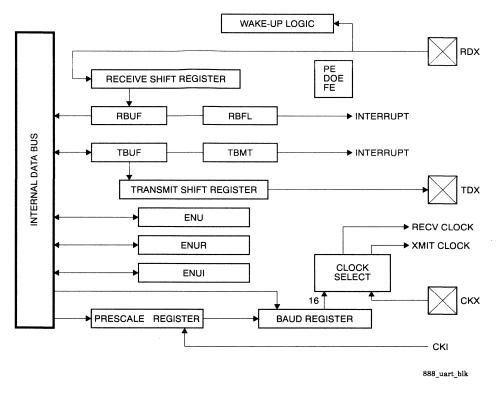

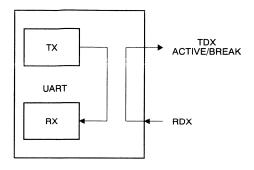

| 11.13         | UART                                    | 11-19        |

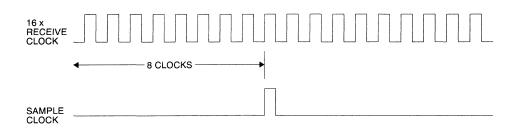

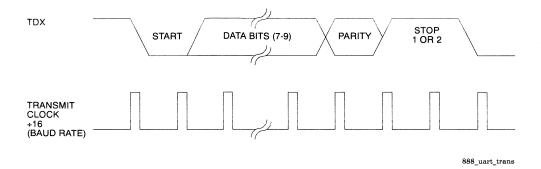

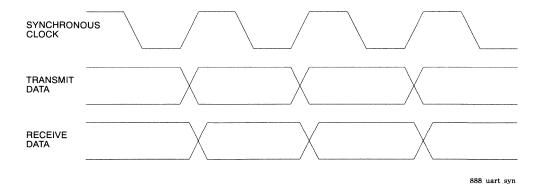

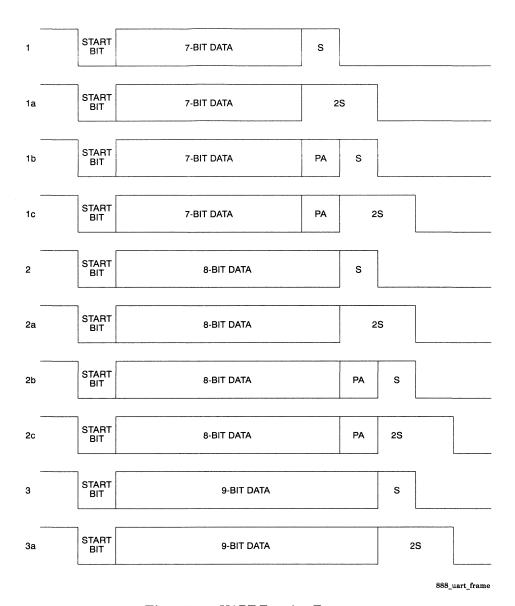

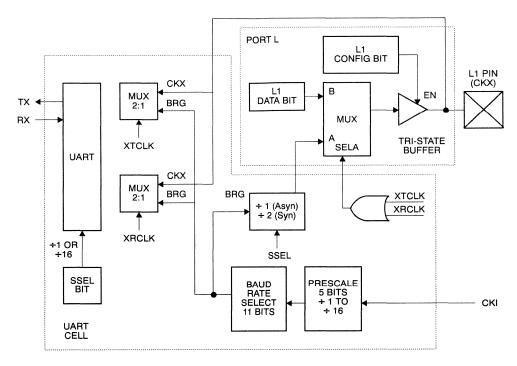

|               | 11.13.1 UART Operation Overview         | 11-19        |

|               | 11.13.2 UART Registers                  | 11-20        |

|               | 11.13.3 UART Interface                  | 11-24        |

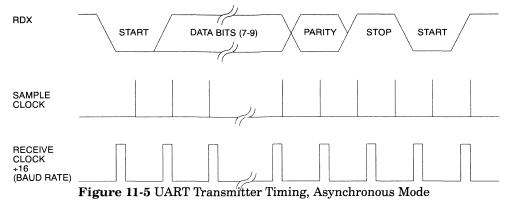

|               | 11.13.4 Asynchronous Mode               | 11-24        |

|               | 11.13.5 Synchronous Mode                | 11-26        |

|               | 11.13.6 Framing Formats                 | 11-27        |

|               | 11.13.7 Reset Initialization            | 11-29        |

|               | 11.13.8 HALT/IDLE Mode Reinitialization | 11-29        |

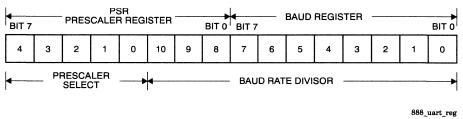

|               | 11.13.9 Baud Clock Generation           | 11-30        |

|               | 11.13.10 UART Interrupts                | 11-36        |

|               | 11.13.11 UART Error Flags               | 11-36        |

|               | 11.13.12 Diagnostic Testing             | 11-37        |

|               | 11.13.13 Attention Mode                 | 11-37        |

|               | 11.13.14 Break Generation and Detection | 11-38        |

| 11.14         | MASK OPTIONS                            | 11-39        |

| 11.15         | EMULATION DEVICES                       | 11-40        |

| Chapter 12    |                                         |              |

| 12.1          | INTRODUCTION                            | 12-1         |

| 12.2      | BLOCK   | DIAGRAM                                      | 12-1           |

|-----------|---------|----------------------------------------------|----------------|

| 12.3      |         | PINOUTS/PACKAGES                             | 12-2           |

| 12.4      | PIN DES | SCRIPTIONS                                   | 12-2           |

| 12.5      |         | OUTPUT PORTS                                 | 12-5           |

| 12.6      |         | AM MEMORY                                    | 12-6           |

| 12.7      |         | EMORY                                        | 12-7           |

| 12.8      |         | ER BIT MAPS                                  | 12-7           |

| 12.9      |         | Y MAP                                        | 12-9           |

| 12.10     |         |                                              | 12-11          |

| 12.11     |         | UPTS                                         | 12-12          |

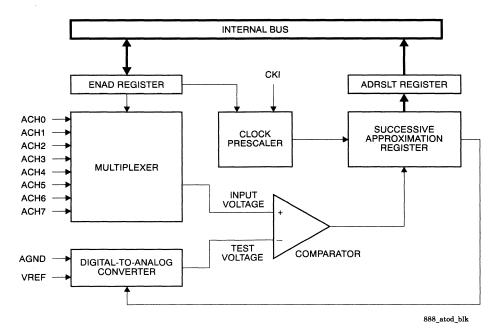

| 12.12     |         | G-TO-DIGITAL CONVERTER                       | 12-13          |

|           | 12.12.1 | A/D Operation                                | 12-13          |

|           | 12.12.2 | A/D Converter Registers                      | 12-14          |

|           | 12.12.3 | Prescaler Selection                          | 12-15          |

|           | 12.12.4 | Single Conversion or Continuous Mode         | 12-16          |

|           | 12.12.5 | Channel Selection                            | 12-16          |

|           | 12.12.6 | Multi-Channel Conversion                     | 12-17          |

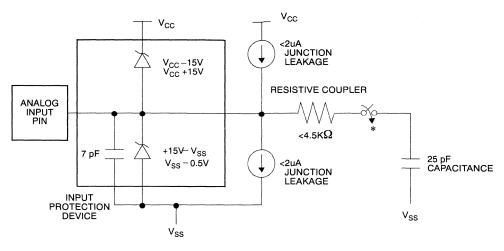

|           | 12.12.7 | Speed, Accuracy, and Hardware Considerations | 12-18          |

| 12.13     |         | PTIONS                                       | 12-19          |

| 12.14     |         | TION DEVICES                                 | 12-20          |

| Chanton 1 |         | LICATION HINTS                               |                |

| Chapter 1 |         |                                              | 10 1           |

| 13.1      |         | OUCTION                                      | 13-1           |

| 13.2      |         | VIRE/PLUS INTERFACE                          | 13-1           |

|           | 13.2.1  | MICROWIRE/PLUS Master/Slave Protocol         | 13-1           |

|           | 13.2.2  | MICROWIRE/PLUS Continuous Mode               | 13-3           |

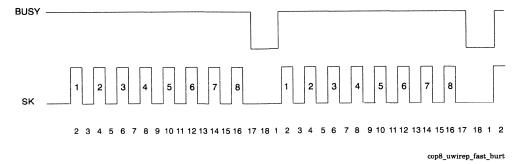

|           | 13.2.3  | MICROWIRE/PLUS Fast Burst Output             | 13-4           |

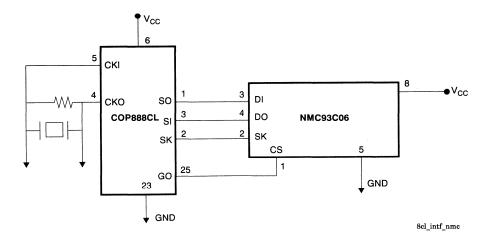

| 10.0      | 13.2.4  | NMC93C06-COP888CL Interface                  | 13-5           |

| 13.3      |         | APPLICATIONS                                 | 13-9           |

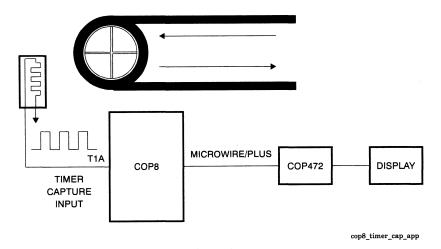

|           | 13.3.1  | Timer Capture Example                        | 13-9           |

| 10.1      | 13.3.2  | External Event Counter Example               | 13-11          |

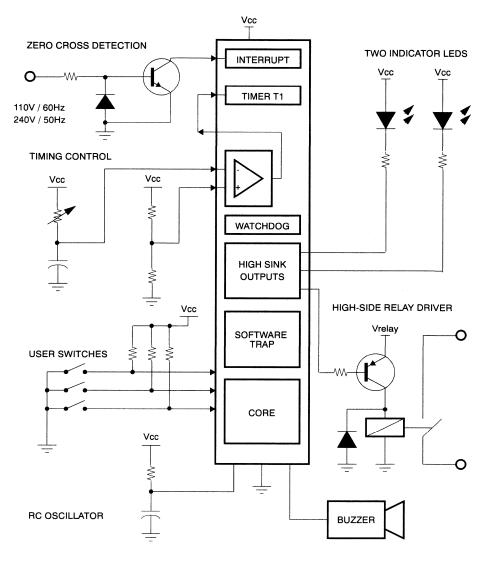

| 13.4      | TRIACC  | CONTROL                                      | 13-11          |

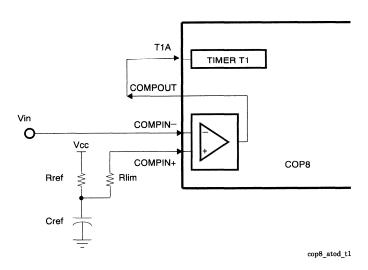

| 13.5      | ANALOG  | G-TO-DIGITAL CONVERSION USING ON-CHIP        | 10.15          |

| 10.0      |         | RATOR                                        | 13-15          |

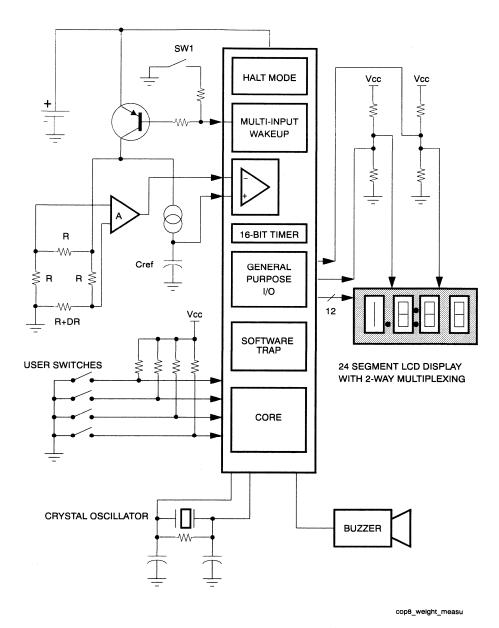

| 13.6      |         | RY-POWERED WEIGHT MEASUREMENT                | 13-17          |

| 13.7      |         | ROSS DETECTION                               | 13-17          |

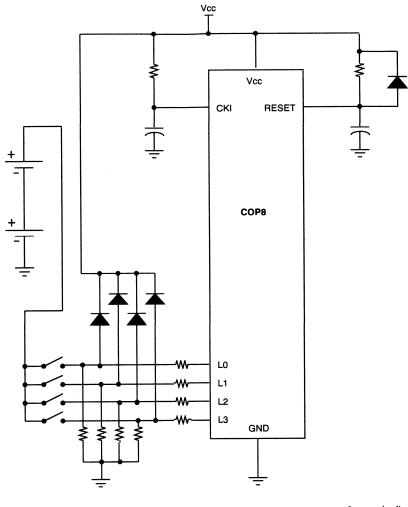

| 13.8      |         | 'RIAL TIMER                                  | 13-19<br>13-21 |

| 13.9      |         |                                              | 13-21          |

|           | 13.9.1  | Clear RAM                                    |                |

|           | 13.9.2  | Binary/BCD Arithmetic Operations             | 13-21          |

|           | 13.9.3  | Binary Multiplication                        | 13-24          |

| 10.10     | 13.9.4  | Binary Division                              | 13-25 $13-27$  |

| 13.10     | EXTERN  | DOG DEGET GIRGUIT                            |                |

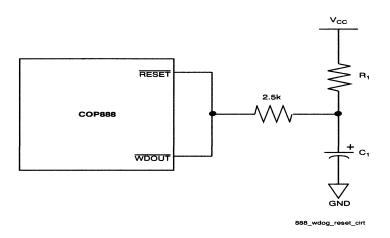

| 13.11     |         | DOG RESET CIRCUIT                            | 13-30          |

| 13.12     |         | PROTECTION ON COP888 PINS                    | 13-30          |

| 13.13     |         | ROMAGNETIC INTERFERENCE (EMI)                | 10.00          |

|           |         | DERATIONS                                    | 13-33          |

|           | 13.13.1 | Introduction                                 | 13-33          |

|           | 13.13.2 | Emission Predictions                         | 13-33          |

|           | 13.13.3 | Board Layout                                 | 13-35          |

|          | 13.13.4<br>13.13.5<br>13.13.6<br>13.13.7 | Decoupling Output Series Resistance Oscillator Control Mechanical Shielding | 13-35<br>13-36<br>13-37<br>13-37 |

|----------|------------------------------------------|-----------------------------------------------------------------------------|----------------------------------|

|          | 13.13.8                                  | Conclusion                                                                  | 13-37                            |

|          |                                          |                                                                             | 10-01                            |

| Appendix | KA DE                                    | VELOPMENT SUPPORT                                                           |                                  |

| A.1      | INTRO                                    | DUCTION                                                                     | A-1                              |

| A.2      | DEVEL                                    | OPMENT HARDWARE                                                             | A-1                              |

|          | A.2.1                                    | COP8 Model 400 In-Circuit Emulator                                          | A-1                              |

|          | A.2.2                                    | COP8 Debug Module                                                           | A-2                              |

|          | A.2.3                                    | Ordering Information                                                        | A-2                              |

| A.3      | DEVEL                                    | OPMENT SOFTWARE                                                             | A-3                              |

|          | A.3.1                                    | COP8 Assembler/Linker/Librarian Package                                     | A-3                              |

|          | A.3.2                                    | COP8 C-Compiler                                                             | A-3                              |

|          | A.3.3                                    | NeuFuz4                                                                     | A-4                              |

| Appendix | k B FO                                   | RM, FIT & FUNCTION EMULATORS                                                |                                  |

| B.1      | EMULA                                    | ATOR DEVICES                                                                | B-1                              |

| B.2      |                                          | ATOR PROGRAMMING                                                            | B-1                              |

| Appendix | k C EL                                   | ECTRICAL CHARACTERIZATION DATA                                              |                                  |

| Appendix | k D TE                                   | CHNICAL SUPPORT                                                             |                                  |

| D.1      | DIREC                                    | Γ TECHNICAL SUPPORT                                                         | D-1                              |

| D.2      |                                          | JR TECHNICAL SUPPORT                                                        | D-1                              |

| Index    |                                          |                                                                             |                                  |

## **LIST OF FIGURES**

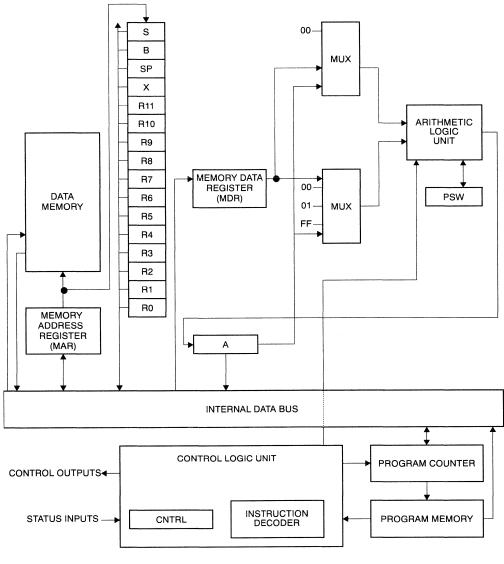

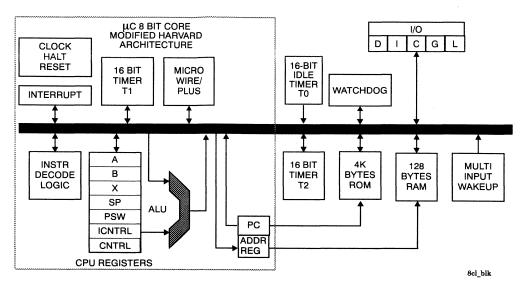

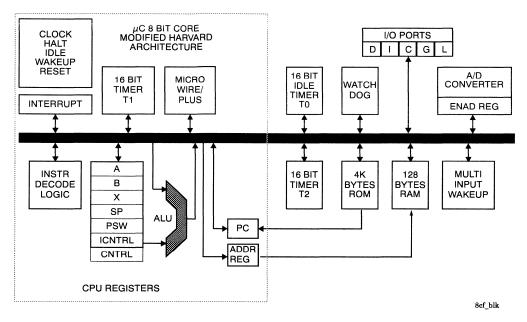

| Figure 2-1  | COP888 Block Diagram                                  | 2-2   |

|-------------|-------------------------------------------------------|-------|

| Figure 2-2  | A Basic Memory Map                                    | 2-4   |

| Figure 2-3  | Memory Map with Data Segment Extension                | 2-6   |

| Figure 2-4  | Control Logic and ALU Interface                       | 2-13  |

| Figure 2-5  | Crystal Oscillator Circuit                            | 2-22  |

| Figure 2-6  | RC Oscillator Circuit                                 | 2-23  |

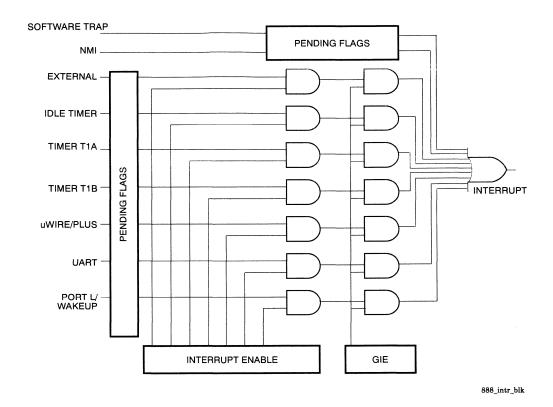

| Figure 3-1  | COP888 Interrupt Block Diagram                        | 3-2   |

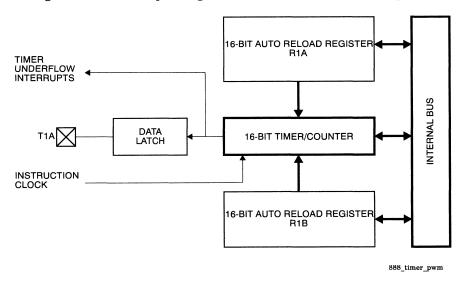

| Figure 4-1  | Timer in PWM Mode                                     | 4-4   |

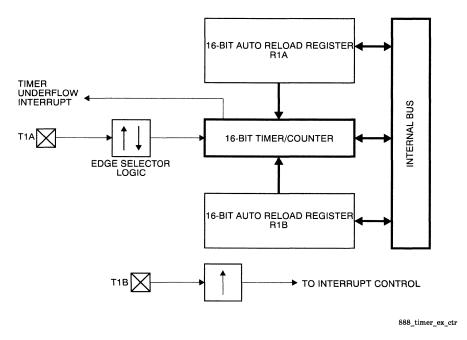

| Figure 4-2  | Timer in External Event Counter Mode                  | 4-6   |

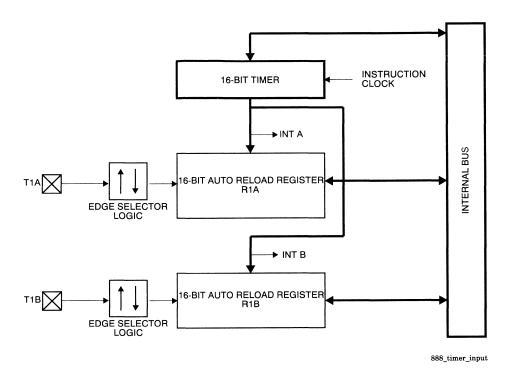

| Figure 4-3  | Timer in Input Capture Mode                           | 4-8   |

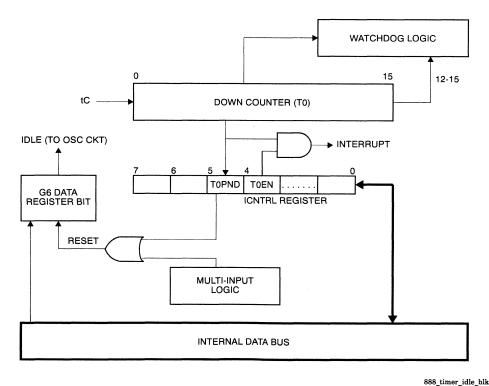

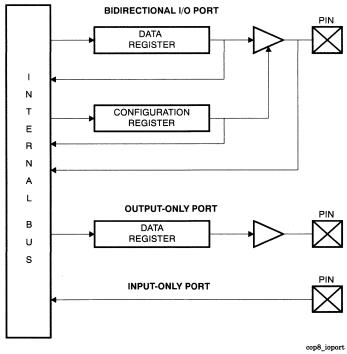

| Figure 4-4  | IDLE Timer (Timer T0) Block Diagram                   | 4-11  |

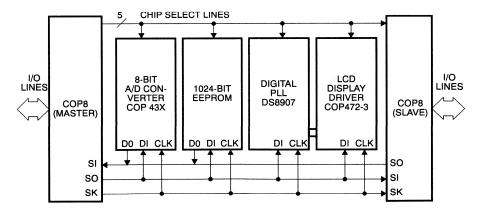

| Figure 5-1  | MICROWIRE/PLUS Example                                | 5-1   |

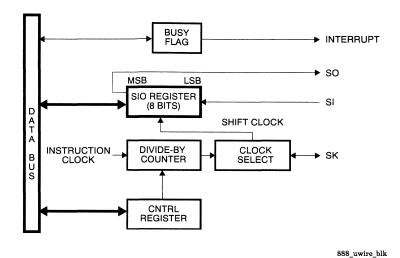

| Figure 5-2  | MICROWIRE/PLUS Circuit Block Diagram                  | 5-2   |

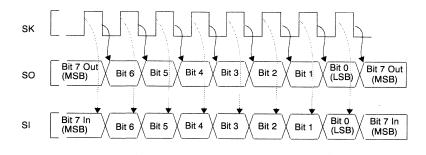

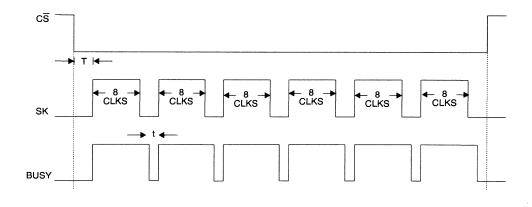

| Figure 5-3  | MICROWIRE/PLUS Interface Timing, Standard SK Mode     | 5-3   |

| Figure 5-4  | MICROWIRE/PLUS Interface Timing, Alternate SK Mode    | 5-3   |

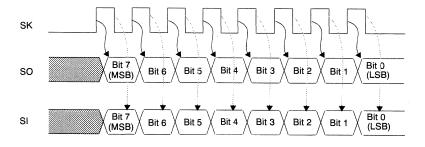

| Figure 7-1  | COP888 Port Structure                                 | 7-1   |

| Figure 7-2  | Multi-Input Wakeup/Interrupt Logic                    | 7-5   |

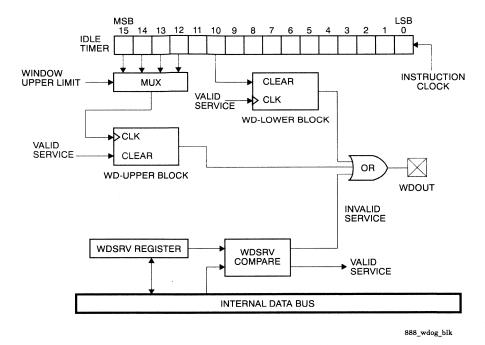

| Figure 8-1  | Watchdog Logic Block Diagram                          | 8-2   |

| Figure 8-2  | Watchdog Service Register (WDSVR) Format              | 8-4   |

|             | COP888CL Block Diagram.                               | 10-2  |

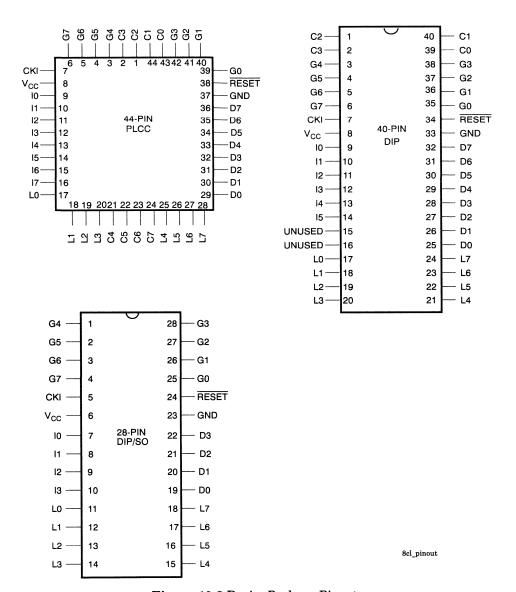

| Figure 10-2 | Device Package Pinouts                                | 10-3  |

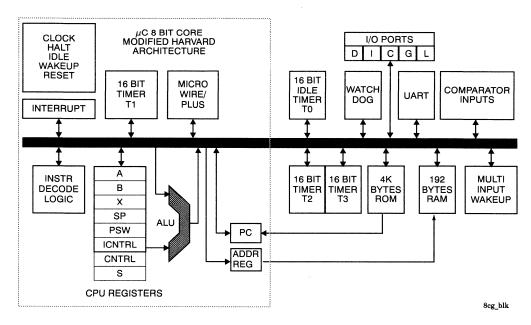

|             | COP888CG Block Diagram                                | 11-2  |

|             | COP888CS Block Diagram                                | 11-3  |

| Figure 11-3 | Device Package Pinouts                                | 11-4  |

| Figure 11-4 | UART Block Diagram                                    | 11-20 |

|             | UART Transmitter Timing, Asynchronous Mode            | 11-25 |

|             | UART Receiver Bit Sampling, Asynchronous Mode         | 11-25 |

| Figure 11-7 | UART Receiver Timing, Asynchronous Mode               | 11-26 |

| Figure 11-8 | UART Synchronous Mode Timing                          | 11-26 |

|             | UART Framing Formats                                  | 11-28 |

|             | OUART Baud Clock Generation Block Diagram             | 11-31 |

|             | LUART Baud Clock Divisor Registers                    | 11-32 |

|             | 2UART Diagnostic Mode Loopback Connection             | 11-38 |

|             | COP888CF Block Diagram                                | 12-2  |

|             | Device Package Pinouts                                | 12-3  |

| Figure 12-3 | COP888CF A/D Converter Block Diagram                  | 12-13 |

|             | A/D Conversion Routine                                | 12-17 |

|             | Analog Input Pin Internal Operation                   | 12-19 |

|             | MICROWIRE/PLUS Sample Protocol Timing                 | 13-2  |

|             | MICROWIRE/PLUS Fast Burt Timing                       | 13-2  |

|             | NMC93C06-COP888CL Interface                           | 13-5  |

|             | Timer Capture Application                             | 13-9  |

|             | A/D Conversion Using On-board Comparator and Timer T1 | 13-15 |

|             | Battery-powered Weight Measurement                    | 13-13 |

|             | Industrial Timer Application                          | 13-16 |

| Figure 10-7 | Power Wakeup Using An NPN Transistor                  | 13-20 |

| Tighte 19-9 | Tower wakeup using An In In Transistor                | 19-79 |

| Figure 13-9 Power Wakeup Using Diodes And Resistors   | 13-29 |

|-------------------------------------------------------|-------|

| Figure 13-10 Watchdog Reset Circuit                   | 13-30 |

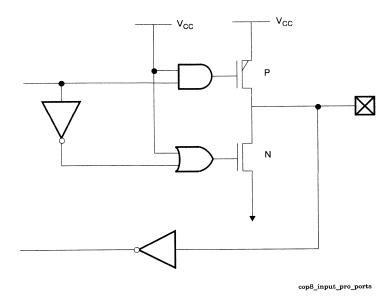

| Figure 13-11 Ports L/C/G Input Protection (Except G6) | 13-31 |

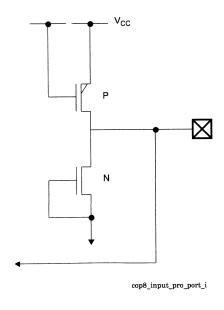

| Figure 13-12 Port I Input Protection                  | 13-31 |

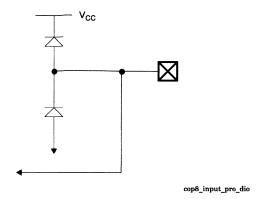

| Figure 13-13 Diode Equivalent of Input Protection     | 13-32 |

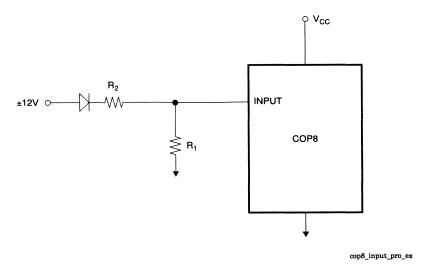

| Figure 13-14 External Protection of Inputs            | 13-33 |

## **LIST OF TABLES**

| Table 1-1   | Features List                                                 | 1-3   |

|-------------|---------------------------------------------------------------|-------|

| Table 2-1   | Data Memory Map                                               | 2-5   |

| Table 2-2   | I/O Port Configuration                                        | 2-8   |

| Table 2-3   | PSW Register Bits                                             | 2-9   |

| Table 2-4   | CNTRL Register Bits                                           | 2-10  |

| Table 2-5   | ICNTRL Register Bits                                          | 2-10  |

| Table 3-1   | Interrupt Vector Table                                        | 3-4   |

| Table 4-1   | Timer Control Bits                                            | 4-2   |

| Table 4-2   | Timer Mode Control Bits                                       | 4-3   |

| Table 5-1   | Port G Configuration Register Bits                            | 5-4   |

| Table 5-2   | Master Mode Clock Select Bits                                 | 5-5   |

| Table 9-1   | Instructions Using A and C                                    | 9-64  |

| Table 9-2   | Transfer of Control Instructions                              | 9-64  |

| Table 9-3   | Memory Transfer Instructions                                  | 9-65  |

| Table 9-4   | Arithmetic and Logic Instructions                             | 9-65  |

| Table 9-5   | Opcodes                                                       | 9-66  |

| Table 10-1  | COP888CL Pinouts                                              | 10-4  |

| Table 10-2  | T2CNTRL, Timer T2 Control Register (Address xxC6)             | 10-7  |

| Table 10-3  | WDSVR, Watchdog Service Register (Address xxC7)               | 10-7  |

| Table 10-4  | ICNTRL, Interrupt Control Register (Address xxE8)             | 10-8  |

| Table 10-5  | CNTRL, Control Register (Address xxEE)                        | 10-8  |

| Table 10-6  | PSW, Processor Status Word Register (Address xxEF)            | 10-8  |

| Table 10-7  | COP888CL Data Memory Map                                      | 10-9  |

| Table 10-8  | COP888CL Interrupt Rank and Vector Addresses                  | 10-12 |

| Table 11-1  | COP888CG/EG/CS Pinouts                                        | 11-5  |

| Table 11-2  | T3CNTRL, Timer T3 Control Register (Address xxB6)*            | 11-8  |

| Table 11-3  | CMPSL, Comparator Select Register (Address xxB7)              | 11-9  |

| Table 11-4  | ENU, UART Control and Status Register (Address xxBA)          | 11-9  |

| Table 11-5  | ENUR, UART Receive Control and Status Register (Address xxBB) | 11-10 |

| Table 11-6  | ENUI, UART Interrupt and Clock Source Register (Address xxBC) | 11-10 |

| Table 11-7  | BAUD, UART Baud Register (Address xxBD)                       | 11-10 |

| Table 11-8  | PSR, UART Prescaler Select Register (Address xxBE)            | 11-11 |

| Table 11-9  | T2CNTRL, Timer T2 Control Register (Address xxC6)             | 11-11 |

| Table 11-10 | WDSVR, Watchdog Service Register (Address xxC7)               | 11-11 |

| Table 11-11 | ICNTRL, Interrupt Control Register (Address xxE8)             | 11-12 |

| Table 11-12 | CNTRL, Control Register (Address xxEE)                        | 11-12 |

| Table 11-13 | PSW, Processor Status Word Register (Address xxEF)            | 11-12 |

|             | COP888CG/EG/CS Data Memory Map                                | 11-13 |

| Table 11-15 | COP888CG/EG/CS Interrupt Rank and Vector Addresses            | 11-17 |

|             | Port I Alternate Functions                                    | 11-18 |

|             | CMPSL, Comparator Select Register (Address xxB7)              | 11-18 |

| Table 11-18 | ENU, UART Control and Status Register (Address xxBA)          | 11-21 |

| Table 11-19 | ENUR, UART Receive Control and Status Register (Address xxBB) | 11-22 |

| Table 11-20 | ENUI, UART Interrupt and Clock Source Register (Address xxBC) | 11-22 |

|             | BAUD, UART Baud Register (Address xxBD)                       | 11-23 |

|             | PSR. UART Prescaler Select Register (Address xxBE)            | 11-23 |

|             | UART Clock Sources (Asynchronous Mode)               | 11-30 |

|-------------|------------------------------------------------------|-------|

| Table 11-24 | UART Clock Sources (Synchronous Mode)                | 11-30 |

| Table 11-25 | UART Prescaler Factors                               | 11-33 |

| Table 11-26 | UART Baud Rate Divisors, 1.8432 MHz Prescaler Output | 11-34 |

| Table 12-1  | COP888CF Pinouts                                     | 12-4  |

| Table 12-2  | T2CNTRL, Timer T2 Control Register (Address xxC6)    | 12-7  |

| Table 12-3  | WDSVR, Watchdog Service Register (Address xxC7)      | 12-7  |

| Table 12-4  | ENAD, A/D Converter Control Register (Address xxCB)  | 12-8  |

| Table 12-5  | ICNTRL, Interrupt Control Register (Address xxE8)    | 12-8  |

| Table 12-6  | CNTRL, Control Register (Address xxEE)               | 12-8  |

| Table 12-7  | PSW, Processor Status Word Register (Address xxEF)   | 12-9  |

| Table 12-8  | COP888CF Data Memory Map                             | 12-9  |

| Table 12-9  | COP888CF Interrupt Rank and Vector Addresses         | 12-12 |

| Table 12-10 | ENAD, A/D Converter Control Register (Address xxCB)  | 12-15 |

| Table 12-11 | A/D Prescaler Options                                | 12-16 |

| Table 12-12 | A/D Channel Selection                                | 12-17 |

| Table 13-1  | Electric Field Calculation Results                   | 13-34 |

| Table A-1   | Assembler/Linker/Librarian ordering information      | A-3   |

| Table A-2   | COP8C Compiler Ordering Information                  | A-4   |

| Table A-3   | NeuFuz4 Ordering Information                         | A-4   |

| Table B-1   | Programmer Information                               | B-1   |

#### 1.1 INTRODUCTION

The COP888 Feature Family 8-bit microcontrollers provide high-performance, low-cost solutions for embedded control applications. COP888 devices are fabricated with National Semiconductor's M²CMOS™ technology for low current drain and a wide operating voltage range. Most instructions are single-byte and have an execution time of one instruction cycle, allowing high throughput. Multiple addressing modes and a rich instruction set further enhance throughput efficiency and reduce program size. Other COP888 features such as reconfigurable inputs and outputs, multi-mode general-purpose timers, and the MICROWIRE/PLUS™ serial interface provide the flexibility needed to construct single-chip solutions for a wide variety of applications.

All COP888 Feature Family members share the set of features listed in Section 1.2. Many individual family members also contain other features such as additional timers, an A-to-D converter, or a UART. The device-specific features are described in Section 1.3.

#### 1.2 BASIC FEATURES

Each member of the COP888 family of microcontrollers offers the following features:

- 8-bit core processor.

- CMOS technology for low power, fully static operation.

- · HALT mode for very low standby power.

- Memory mapped architecture. All RAM, I/O ports, and registers (except A and PC) are mapped into the data memory address space.

- On-chip data memory and program memory.

- Flexible, reconfigurable I/O.

- MICROWIRE/PLUS serial interface, a 3-wire serial data communication system

that allows the microcontroller to be programmed for either master or slave mode

operation.

- Extremely versatile 16-bit timer with two associated autoload/capture registers, which can operate in any of three modes: PWM (Pulse Width Modulation), external event counter, or input capture register.

- Non-maskable Software Trap interrupt.

- Maskable interrupts (number and type depending on family member).

- Two 8-bit "Register Indirect" data memory pointers.

- 8-bit Stack Pointer (SP) for stack in data memory RAM.

- Choice of clock types: crystal oscillator, or R/C oscillator.

#### 1.3 DEVICE-SPECIFIC FEATURES

In addition to the core features, non-core features are provided by specific COP888 devices. These features are:

- · 8-bit Data Segment Address Register (S Register), used for addressing data memory beyond the first 128 bytes of RAM

- One or more additional 16-bit general-purpose timers

- IDLE mode for very low standby power while maintaining real time with associated IDLE Timer

- · Multi-Input Wakeup/Interrupt feature, which provides additional inputs for interrupts or to exit the HALT or IDLE mode

- · Watchdog and clock monitor

- NMI non-maskable interrupt

- Full-duplex, double-buffered UART (Universal Asynchronous Receiver/Transmitter) for serial communication

- Analog-to-Digital (A/D) Converter with eight single-ended or four differential-pair channels

Table 1-1 lists the available COP888 device types and shows the features present in each device. The device types are listed across the top, and the features are listed along the left side. Inside the table, the word "YES" or a numerical quantity indicates the presence of that feature; a dash indicates the absence of a feature. Memory sizes are expressed in bytes.

Table 1-1 Features List

| Feature                       | COP888CL | COP888CG | COP888CF | COP888EG | COP888CS |

|-------------------------------|----------|----------|----------|----------|----------|

| Program Memory (ROM)          | 4K       | 4K       | 4K       | 8K       | 4K       |

| Data Memory (RAM)             | 128      | 192      | 128      | 256      | 192      |

| S-Register                    |          | YES      |          | YES      | YES      |

| 16-Bit Programmable<br>Timers | 2        | 3        | 2        | 3        | 1        |

| IDLE Mode and Timer           | YES      | YES      | YES      | YES      | YES      |

| MIWU Register                 | YES      | YES      | YES      | YES      | YES      |

| Watchdog and Clock<br>Monitor | YES      | YES      | YES      | YES      | YES      |

| UART                          |          | YES      |          | YES      | YES      |

| Comparator                    |          | 2        |          | 2        | 1        |

| A/D Converter                 |          |          | YES      | <u> </u> | _        |

## **ARCHITECTURE**

#### 2.1 INTRODUCTION

The COP888 microcontroller contains all program memory and data memory internally. In addition, it contains on-chip configurable I/Os, an on-chip timer, and a built-in MICROWIRE/PLUS interface. The presence of on-chip memory and peripherals allows the COP888 microcontroller to provide a single-chip solution for many applications.

The COP888 memory organization is based on the "Harvard" architecture, in which the program memory is distinct from the data memory. Each of these two types of memory has its own physical memory space, and uses its own internal address bus. The advantage of this type of organization is that accesses to program memory and data memory can take place concurrently, reducing overall execution time. By contrast, in the "Von Neumann" architecture, program memory and data memory share the same address bus, and concurrent accesses cannot occur.

Except for the Accumulator (A) and Program Counter (PC), all registers, I/O ports, and RAM are memory mapped in the data memory address space. Among these registers are the B Register, X Register, Stack Pointer (SP), and I/O port registers. All such registers can be accessed by reading or writing their memory addresses.

The COP888 architecture provides one enhancement to the Harvard architecture: an instruction called Load Accumulator Indirect (LAID), which allows access to data tables stored in program memory. A conventional Harvard architecture does not allow this.

The COP888 device communicates with other devices through several configurable I/O ports or through the MICROWIRE/PLUS serial I/O interface. The I/O ports are designated by letter names, such as Port C, Port D, Port G, Port I, and Port L.

A 16-bit general-purpose timer is provided in all COP888 microcontrollers, together with two associated 16-bit autoload/capture registers. The timer can be configured to operate in any of three modes: Pulse Width Modulation (PWM), external event counter, or input capture mode.

A maximum of sixteen different interrupts are available in the COP888: two non-maskable interrupts and 14 maskable interrupts. All interrupts cause a branch to the same location in program memory. A special instruction (VIS) may be placed at this location to force an automatic branch to the highest priority-interrupt service routine.

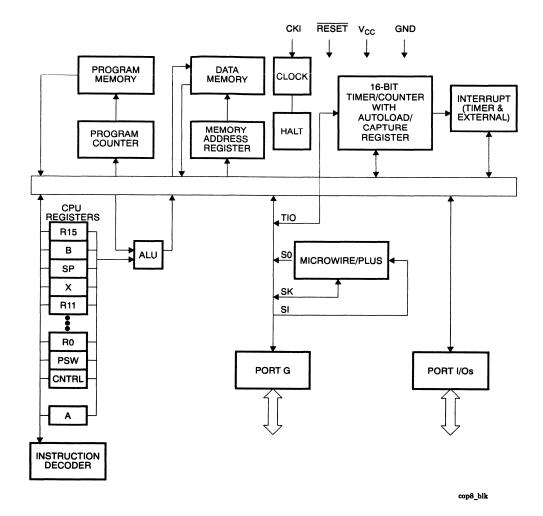

#### 2.2 BLOCK DIAGRAM

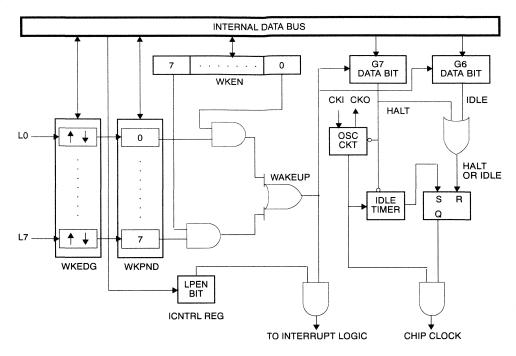

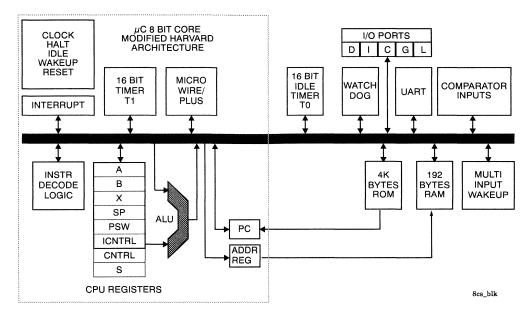

A block diagram of the COP888 Family architecture is shown in Figure 2-1. All COP888 Family devices contain the elements pictured in the block diagram. These elements include: the Arithmetic Logic Unit (ALU), Data Memory, Program Memory, Timer 1, MICROWIRE/PLUS, Port I/Os, and Interrupt Logic. Functional blocks not common to all

Figure 2-1 COP888 Block Diagram

COP888 Family members are not shown in Figure 2-1. Block diagrams of individual devices are shown in the device-specific chapters of this manual.

#### 2.3 MEMORY ORGANIZATION

The COP888 microcontrollers are based on a modified Harvard-style architecture. This type of architecture separates the control program memory from the data memory. Each memory type has its own address space, address bus and data bus. The following sections describe the memory structure.

#### 2.3.1 Program Memory

The COP888 program memory is a block of byte-wide non-volatile ROM or EPROM memory. The program memory addressing range is 32 Kbytes. A 15-bit Program Counter (PC) is used to address the program memory, which is subdivided into 4-Kbyte segments with respect to certain instructions. The program memory may hold program instructions or constant data.

The 4-Kbyte segment divisions within the program memory affect the economical 2-byte Jump Absolute (JMP) and Jump Subroutine (JSR) instructions. These instructions cause the lower 12-bits of the PC to be replaced by the value specified in the instruction while the upper three bits remain unchanged. Thus, these instructions branch only within the currently addressed 4-Kbyte program memory segment.

The indirect instructions, Jump Indirect (JID) and Load Accumulator Indirect (LAID), operate only within a program memory block of 256 bytes. This restriction exists because only the lower eight bits of the PC (PCL) are replaced during program memory table lookups. The upper seven bits of the PC (PCU) remain unchanged. Replacing only the PCL minimizes the execution time of this instruction. Programmers must ensure that LAID/JID instructions and their associated tables do not cross the 256-byte program memory boundaries.

The very economical Jump Relative Short (JP) instruction is completely independent of all program memory block and memory segment boundaries. This single-byte JP instruction allows a branch forward of up to 32 locations or backwards of up to 31 locations relative to the current contents of the program counter. A branch forward of 1 is not allowed, since this may be implemented with a NOP.

## 2.3.2 Data Memory

All COP888 family members have read/write data memory. Some sections of the data memory space are reserved for the CPU registers, I/O registers, and control registers, all of which are memory mapped. Other sections of the data memory contain RAM and/or EEPROM, which can be used by the application program. The amount of available RAM or EEPROM memory varies from one family member to another. For information on the quantity and type of data memory, see the device-specific chapters later in this manual.

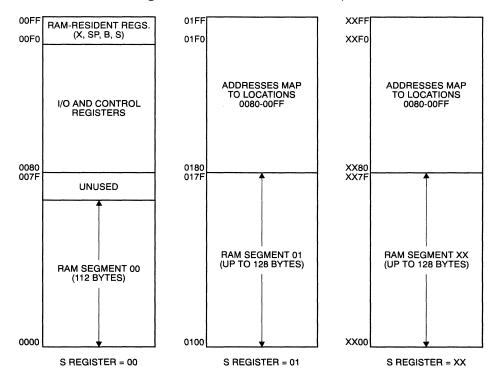

Data memory can be accessed either directly by an address specified in the instruction, or indirectly using the X, SP, or B pointer registers. In all cases, the data memory location is specified as a single byte. Thus, one of 256 memory locations is specified for a data memory access. In the most basic COP888 devices, only the first 256 bytes of data memory are used. In other COP888 devices, a data segment extension register (S register) extends the data memory address range to 32 Kbytes. Data memory extension using the S register is explained in the next section of this manual, Data Segment Extension.

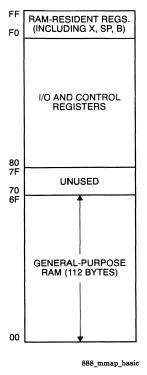

In basic devices that do not use data segment extension, there is a single 256-byte segment of data memory, divided into smaller segments as shown in Figure 2-2. There are 128 bytes of RAM, occupying two non-contiguous address spaces: 112 bytes of lower memory, from 00 to 6F Hex, and 16 bytes at the top of the memory, from F0 to FF Hex. Most of the remaining upper part of this memory, from B0 through EF Hex, is used for

the I/O and control registers required by the timers, ports, MICROWIRE interface, CPU core, and optional COP888 peripherals (UART, comparator, etc.). The remaining parts of the 256-byte memory segment (70-7F Hex) are not used.

Figure 2-2 A Basic Memory Map

The lower, 112-byte segment of RAM is general-purpose read/write memory that is available to the application program. Upon reset, the stack pointer is initialized to the top of this segment (6F Hex), and the stack grows downward from that address as items are pushed onto the stack. Memory from 00 Hex up to the stack can be used for any purpose by the application program. The first 16 addresses (00-0F Hex) have special significance when used with certain instructions (such as LD B,#), because then the instructions are single byte and take only one instruction cycle to execute, rather than two bytes and two instruction cycles.

The upper, 16-byte segment of RAM at the top of memory is used for the RAM-resident registers. The X, SP, and B pointer registers are mapped into memory locations FC, FD, and FE Hex, respectively. The S register, if used, is mapped into address FF Hex. The remaining 12 register locations are available to the application program for any purpose. Certain COP888 instructions (such as DRSZ) work only with this 16-byte segment of memory. Certain other instructions (such as LD MD,#) are more efficient when used with this 16-byte segment than with other RAM memory locations.

There is at least one segment of unused data: 16 bytes from 70 to 7F Hex. Reading from this unused segment returns FF Hex. Reading from other unused segments returns unknown data.

All RAM, I/O ports, and registers (except A and PC) are mapped into the data memory address space. Table 2-1 shows a basic Register Memory Map for all COP888 devices. Refer to the device-specific chapters for complete memory maps of individual devices.

Table 2-1 Data Memory Map

| Address   | Contents                                   |

|-----------|--------------------------------------------|

| 00–6F     | On-chip RAM Address Space                  |

| 70–BF     | On-chip Data Memory Address Space          |

| C0-CF     | I/O and Register Address Space             |

| D0        | Port L Data Register                       |

| D1        | Port L Configuration Register              |

| D2        | Port L Input Pins (read only)              |

| D3        | Reserved for Port L                        |

| <b>D4</b> | Port G Data Register                       |

| D5        | Port G Configuration Register              |

| D6        | Port G Input Pins (read only)              |

| D7        | Port I Input Pins (read only)              |

| D8        | Port C Data Register                       |

| D9        | Port C Configuration Register              |

| DA        | Port C Input Pins (read only)              |